题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

试用集成4位二进制加法计数器74LS161构成十一进制计数器。 (1)用反馈复位法实现。 (2)用反馈置数法实现。

试用集成4位二进制加法计数器74LS161构成十二进制计数器。

(1)用反馈复位法实现。

(2)用反馈置数法实现。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

试用集成4位二进制加法计数器74LS161构成十二进制计数器。

(1)用反馈复位法实现。

(2)用反馈置数法实现。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试用集成4位二进制加法计数器74LS161构成十一进制计数器…”相关的问题

更多“试用集成4位二进制加法计数器74LS161构成十一进制计数器…”相关的问题

中规模集成同步4位二进制加法计数器74LS161的功能表如下表所示,要求:

| CP | bar{CR}bar{LD} | CTPCTT | D0D1D2D3 | Q0n+1Q1n+1Q2n+1Q3n+1 |

| × | 0 × | × × | × × × × | 0 0 0 0 |

| ↑ | 1 0 | × × | d0d1d2d3 | d0d1d2d3 |

| × | 1 1 | 0 × | × × × × | 保 持 |

| × | 1 1 | × 0 | × × × × | 保 持 |

| ↑ | 1 1 | 1 1 | × × × × | 4位二进制加法计数器 进位输出:CO=CTTQ3Q2Q1Q0 |

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

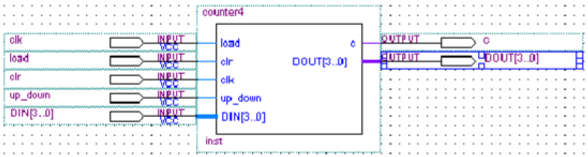

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。

试用 Verilog语言描述一个4位二进制可逆计数器的行为。要求如下:

(1)电路具有5种功能,即异步清零、同步置数、递增计数、递减计数和保持原有状态不变。且要求计数器能输出进位信号和借位信号,即当计数器递增计数到最大值时,产生一个高平有效的进位信号C0;当计数器递减计数到最小值0时,产生一个高电平有效的借位信号B0。

(2)用QuartusI软件进行逻辑功能仿真,并给出仿真波形。

由16×4位ROM和4位二进制加法计数器74LS161组成的脉冲分配电路如图7-13所示,ROM输入和输出关系如表7-4所示。试画出在CLK信号作用下D3、D2、D1、D0的波形。

表7-4 R0M输入和输出关系 | |||||||

| 地址输入 | 数据输出 | ||||||

| A3 | A2 | A1 | A0 | D3 | D2 | D1 | D0 |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 1 0 0 0 0 1 1 1 1 1 0 0 0 0 0 0 | 1 0 0 1 1 0 0 0 1 1 0 0 0 1 1 0 | 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 | 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |