更多“定时器/计数器输出信号OUT输出高电平信号时,表明_____…”相关的问题

更多“定时器/计数器输出信号OUT输出高电平信号时,表明_____…”相关的问题

试用 Verilog语言描述一个4位二进制可逆计数器的行为。要求如下:

(1)电路具有5种功能,即异步清零、同步置数、递增计数、递减计数和保持原有状态不变。且要求计数器能输出进位信号和借位信号,即当计数器递增计数到最大值时,产生一个高平有效的进位信号C0;当计数器递减计数到最小值0时,产生一个高电平有效的借位信号B0。

(2)用QuartusI软件进行逻辑功能仿真,并给出仿真波形。

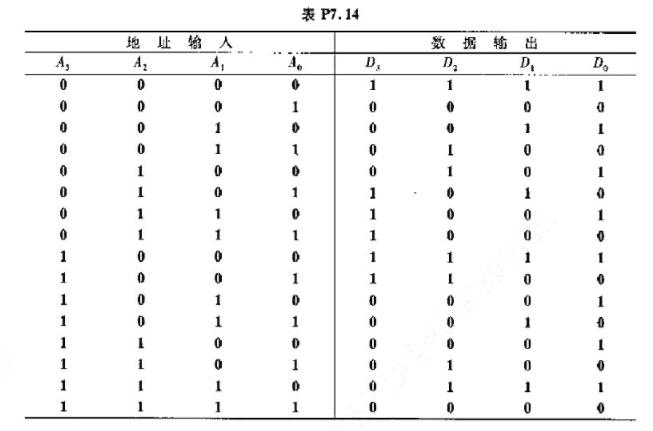

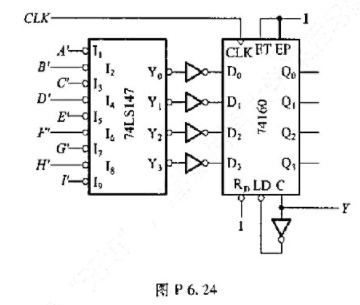

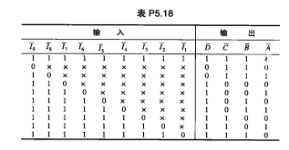

图P5.18是由二进制优先权编码器CT74LS147(真值表参见表P5.18)和同步十进制加法计数器CT74160组成的可控分频器.试说明当输入控制信号

分别为低电平,并假定CP脉冲的频率为f0时,由Z端输出的脉冲的频率是多少?

分别为低电平,并假定CP脉冲的频率为f0时,由Z端输出的脉冲的频率是多少?

列出下述问题的真值表,并写出逻辑表达式

①有A、B、C三个输入信号,如果三个输入信号均为0或其中一个为1时,输出信号Y=1,其余情况下,输出Y=0;

②有A、B、C三个输入信号,当三个输入信号出现奇数个1时,输出为1,其余情况下输出为0(这是奇校验的校验位生成器);

③有三个温度探测器,当某个温度探测器的温度超过60℃时,输出信号为1,否则输出信号为0。当有两个或两个以上的温度探测器的输出信号为1时,总控制器输出信号为1,白动控制调控设备使温度降低到60℃以下。试写出总控制器的真值表和逻辑表达式。

若输入信号为 为使输出信号中分别包含以下频率成分:

为使输出信号中分别包含以下频率成分:

(1) ;

;

(2) ;

;

(3)直流.

请你分别设计相应的系统(尽可能简单)满足此要求,给出系统输出与输入的约束关系式.讨论这三种要求有何共同性、相应的系统有何共同性.

A.输出低电平电流、输入低电平电流

B.输入高电平电流、输出低电平电流

C.输出高电平电流、输出低电平电流

D.输出高电平电流、输入高电平电流

有一线性时不变系统的单位抽样响应为h(n),输入信号为x(n),若

用两种方法求该系统的输出信号y(n):(a)直接求线性卷积(b)用z变换求。

如果结果不匹配,请

如果结果不匹配,请