题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

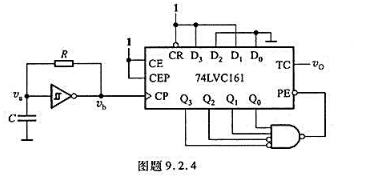

集成施密特触发器和4位同步二进制加法器74LVC161组成的电路如图题9.2.4所示。(1)分别说明图中两

集成施密特触发器和4位同步二进制加法器74LVC161组成的电路如图题9.2.4所示。(1)分别说明图中两

集成施密特触发器和4位同步二进制加法器74LVC161组成的电路如图题9.2.4所示。

(1)分别说明图中两部分电路的功能;

(2)画出图中74LVC161组成的电路的状态图;

(3)画出图中va、vb和v0的对应波形。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“集成施密特触发器和4位同步二进制加法器74LVC161组成的…”相关的问题

更多“集成施密特触发器和4位同步二进制加法器74LVC161组成的…”相关的问题